Еволюція транзисторів: від планарних до CFET, 3D-інтеграція переосмислює прогрес напівпровідників

Понад півстоліття напівпровідникова промисловість розвивалася, дотримуючись одного простого правила: робіть транзистори меншими.Зменшення розмірів функцій забезпечило вищу продуктивність, меншу потужність і меншу вартість транзистора.Але сьогодні цей шлях досяг своєї фізичної та економічної межі.Епоха чистого масштабування закінчилася, і настала нова ера структурні інновації та 3D інтеграція почалося.

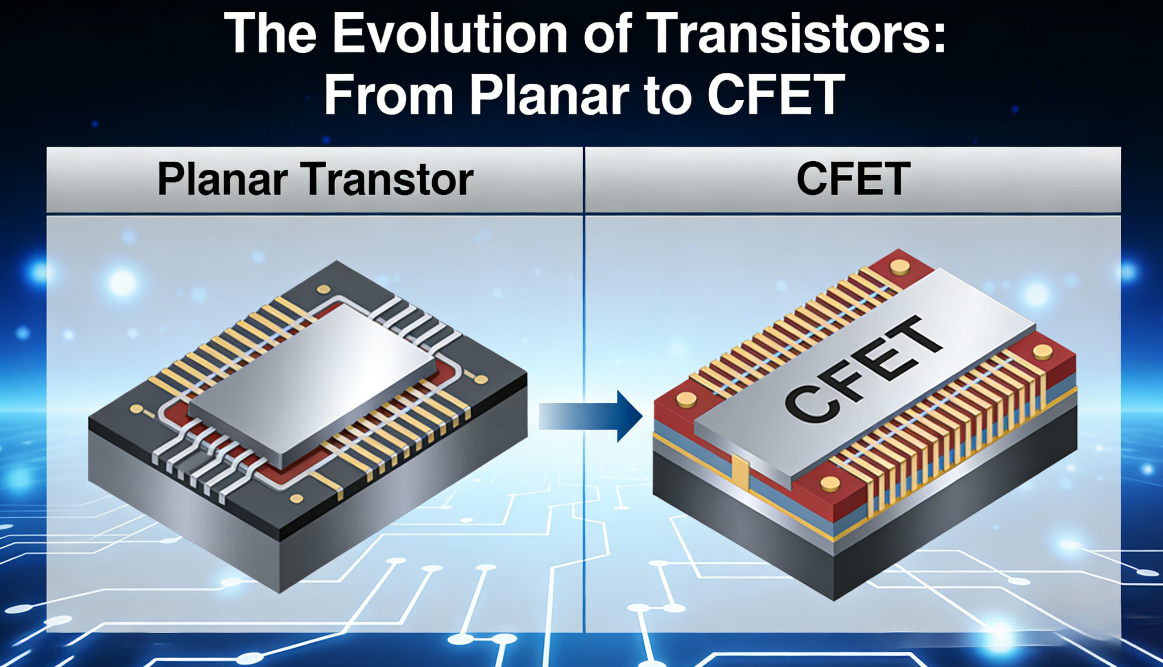

Сам транзистор переживає повну архітектурну революцію.Від плоского MOSFET до FinFET, від GAA нанолистів до CFET укладання, кожен крок являє собою перехід від стиснення до перебудова транзистора в трьох вимірах.Це не просто поступове вдосконалення — це повне визначення того, як чіпи забезпечують продуктивність.

Чотири покоління транзисторної архітектури

1. Планарний транзистор (традиційний 2D)

Класична плоска конструкція, де ворота контролюють канал зверху.Він домінував з перших днів аж до 40 нм і 28 нм.У міру подальшого зменшення розмірів струм витоку та електростатичний контроль стали нерозв’язними проблемами.

2. FinFET (3D Gate Control)

Канал стає вертикальним «плавцем», з воротами, що обертаються навколо трьох сторін.Це суттєво покращує електростатичний контроль, зменшує витік і дозволяє зменшити масштаб до 7 нм, 5 нм і навіть 3 нм.FinFET став основою сучасної ери високопродуктивних мікросхем.

3. GAA Nanosheet (Gate-All-Around)

На 2 нм і нижче FinFET досягає своєї межі.GAA замінює ребро складеними горизонтальними нанодротами або листами, повністю оточеними затвором.Це забезпечує кращий контроль, меншу потужність і вищий струм приводу.GAA тепер є основною структурою для чіпів класу 2 нм у TSMC, Samsung і Intel.

4. CFET (додатковий FET)

Наступний рубіж: укладання NMOS і PMOS вертикально.CFET поміщає два транзистори в один, різко зменшуючи площу та покращуючи щільність.Це остаточний еволюційний кінець масштабування транзисторів до того, як справжня 3D системна інтеграція візьме верх.

Чому лише масштабування більше не працює

- Вартість процесу зростає експоненціально з кожним новим вузлом

- Квантовий витік і фізичні обмеження посилюють обмеження

- Затримка з'єднання та споживання енергії випереджають швидкість транзистора

- Великі монолітні чіпи страждають від низького виходу і високої вартості

Індустрія зрозуміла: продуктивність більше не залежить від менших транзисторів.Це походить від кращі з’єднання, розумніша архітектура та вертикальна інтеграція.

Нова ера: три рівні 3D-інновацій

Розвиток напівпровідників тепер визначається трьома вимірами 3D-дизайну:

- 3D транзистор: FinFET, GAA, CFET – побудова транзистора вертикально

- Тривимірне стекування пристроїв: Логічна пам'ять, гібридне зв'язування, стекування SRAM

- 3D системна інтеграція: мікросхема, 2.5D/3D упаковка, інтеграція на основі інтерпозера

Разом вони утворюють 3D×3D×3D епохи: транзистор, пристрій і система стають тривимірними.

DTCO: нова основна компетенція

Коли масштабування закінчується, Кооптимізація технологій проектування (DTCO) стає критичним.Це означає спільне проектування архітектури, структури транзистора, прокладки металу та упаковки з самого початку.Найсильніші компанії більше не просто лідери процесів — вони є інтеграторами системного рівня.

Ефективність проводки, подача електроенергії, тепловий дизайн і щільність смуги тепер визначають реальну продуктивність продукту.

AI є головною рушійною силою

ШІ та високопродуктивні обчислення вимагають безпрецедентної пропускної здатності, енергоефективності та щільності.Ці вимоги не можуть бути виконані традиційним масштабуванням.Вони вимагають:

- Надвисока пропускна здатність між пам'яттю та комп'ютером

- Надзвичайна енергоефективність на операцію

- Масовий паралелізм і щільна інтеграція

ШІ змусив всю галузь відмовитися від чистого масштабування та прийняти повну 3D-гетерогенну інтеграцію.

Висновок: майбутнє не менше, воно вище

Епоха скорочення транзисторів відходить у минуле.Майбутнє напівпровідників — це не створення менших пристроїв, а створення систем вищий, щільніший і розумніший зв’язок.

Від Planar до FinFET і GAA до CFET транзистор завершив свою еволюцію.Наступний бій відбудеться 3D-інтеграція, вдосконалене пакування та дизайн на системному рівні.Саме тут вирішиться наступне десятиліття лідерства в галузі напівпровідників.